**Managing Editor Publisher Content Architect**

Richard Bowles Stuart Douglas Daniel Aarno Jakob Engblom

**Program Manager Technical Editor Technical Illustrators**

Stuart Douglas David Clark MPS Limited

# **Technical and Strategic Reviewers**

Daniel Aarno Jakob Engblom

## **Intel Technology Journal**

Copyright © 2013 Intel Corporation. All rights reserved. ISBN 978-1-934053-62-1, ISSN 1535-864X

Intel Technology Journal Volume 17, Issue 2

No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except as permitted under Sections 107 or 108 of the 1976 United States Copyright Act, without either the prior written permission of the Publisher, or authorization through payment of the appropriate per-copy fee to the Copyright Clearance Center, 222 Rosewood Drive, Danvers, MA 01923, (978) 750-8400, fax (978) 750-4744. Requests to the Publisher for permission should be addressed to the Publisher, Intel Press, Intel Corporation, 2111 NE 25th Avenue, JF3-330, Hillsboro, OR 97124-5961. E-Mail: intelpress@intel.com.

This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold with the understanding that the publisher is not engaged in professional services. If professional advice or other expert assistance is required, the services of a competent professional person should be sought. Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents,

trademarks, copyrights, or other intellectual property rights.

Intel may make changes to specifications, product descriptions, and plans at any time, without notice.

Fictitious names of companies, products, people, characters, and/or data mentioned herein are not intended to represent any real individual, company, product, or event. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications. Intel, the Intel logo, Intel Atom, Intel AVX, Intel Battery Life Analyzer, Intel Compiler, Intel Core i3, Intel Core i5, Intel Core i7, Intel DPST, Intel Energy Checker, Intel Mobile Platform SDK, Intel Intelligent Power Node Manager, Intel QuickPath Interconnect, Intel Rapid Memory Power Management (Intel RMPM), Intel VTune Amplifier, and Intel Xeon are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products.

For more complete information about performance and benchmark results, visit www.intel.com/benchmarks

<sup>†</sup>Other names and brands may be claimed as the property of others.

This book is printed on acid-free paper.

Publisher: Richard Bowles Managing Editor: Stuart Douglas

Library of Congress Cataloging in Publication Data:

Printed in China 10 9 8 7 6 5 4 3 2 1

First printing: October 2013

#### Notices and Disclaimers

ALL INFORMATION PROVIDED WITHIN OR OTHERWISE ASSOCIATED WITH THIS PUBLICATION INCLUDING, INTER ALIA, ALL SOFTWARE CODE, IS PROVIDED "AS IS", AND FOR EDUCATIONAL PURPOSES ONLY. INTEL RETAINS ALL OWNERSHIP INTEREST IN ANY INTELLECTUAL PROPERTY RIGHTS ASSOCIATED WITH THIS INFORMATION AND NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHT IS GRANTED BY THIS PUBLICATION OR AS A RESULT OF YOUR PURCHASE THEREOF INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THIS INFORMATION INCLUDING, BY WAY OF EXAMPLE AND NOT LIMITATION, LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR THE INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT ANYWHERE IN THE WORLD.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products.

#### For more information go to http://www.intel.com/performance

Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice.

Notice revision #20110804

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm

# INTEL® TECHNOLOGY JOURNAL SIMICS UNLEASHED – APPLICATIONS OF VIRTUAL PLATFORMS

# **Articles**

| Foreword Simics*—The Early Years                                                                                                   | 7   |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| Simics* Overview                                                                                                                   | 8   |

| Using Virtual Platforms for BIOS Development and Validation                                                                        | 32  |

| Simics*–SystemC* Integration.                                                                                                      | 54  |

| Post-Silicon Impact: Simics* Helps the Next Generation of Network Transformation and Migration to a Software-Defined Network (SDN) | 66  |

| Landslide: A Simics* Extension for Dynamic Testing of Kernel Concurrency Errors                                                    | 84  |

| Early Hardware Register Validation with Simics*                                                                                    | 102 |

| Software Power and Performance Correlation on Simics*                                                                              | 114 |

| Simics* on Shared Computing Clusters: The Practical Experience of Integration and Scalability                                      | 126 |

| Device Driver Synthesis                                                                                                            | 138 |

| Using Simics in Education                                                                                                          | 160 |

| Sim-O/C: An Observable and Controllable Testing Framework for Flusive Faults                                                       | 180 |

# Foreword Simics\*—The Early Years

#### Peter S. Magnusson,

Engineering Director, Google, Inc.

When I interviewed for an internship at the Swedish Institute of Computer Science (SICS) in 1991, the project was to write a parallel-computer simulator for the Data Diffusion Machine (DDM) research effort being led by Seif Haridi and Erik Hagersten. I was hired by Andrzej Ciepielewski and Torbjörn Granlund and the project was supposed to take six weeks. It took a little longer than that.

Back in the 1980s, it was common for computer architecture research to be entirely based on simulations running computationally intensive workloads—traditional high performance computing. The best practice in the field was summarized by the release of the Stanford Parallel Applications for Shared Memory (SPLASH) benchmark suite—which coincidentally also occurred in 1991.

However, at the time (late 1980s, early 1990s), a number of research groups recognized that much of parallel-computer usage was not compute-intensive as much as it was data-intensive—for example, transactional workloads, better represented by benchmarks like TPC-C. But these workloads were generally commercial software, large parts of which were only available in binary. They also heavily relied on the underlying operating system.

So a project was conceived to develop a simulator to both support the computer architecture work around the DDM project and also support porting an operating system to the prototype. An existing, groundbreaking simulation environment developed by Robert Bedichek at the University of Washington was extended to support a multiprocessor system and to mimic real devices.

(As a curious aside to the reader, Robert's work on simulation began at his time at Intel in the late 1980s, so Simics now being an Intel product closes the loop.)

The six weeks grew. Some six calendar years, twenty man years, and several hundred thousand lines of code later, in 1997, the simulation group in the Computer and Network Architectures (CNA) group at SICS finally succeeded in the original goal: booting a commercial operating system (Solaris\* 2.6) on a simulated Sun Microsystems server (sun4m architecture). This was the first known occasion of an academic group running an unmodified commercial operating system in a fully simulated environment. The "full system simulator" was born.

The simulation group at SICS eventually grew to five people, all of whom became founding employees of Virtutech in 1998: Magnus Christensson, Fredrik Larsson, Peter Magnusson, Andreas Moestedt, and Bengt Werner. Our first customers were Sun Microsystems, Ericsson, and HP. To the original SPARC\* V8 architecture, we added SPARC V9, x86, x86-64, Power, ARM, Itanium®, and so on. We invented a number of new technologies and tools along the way, making Simics by far the most capable tool in its field.

With the launch of Simics 3.0 and the Hindsight\* technology in 2005, all the core elements that I remember scoping out on a whiteboard around 1993 were in place, and several I hadn't imagined. So in some sense, it became a software project that literally took over 100 times longer than originally planned.

In the process I became convinced (and still am) that this is by far the best way forward to improve software development environments, since, once inside a deterministic simulator, you can do some very interesting things.

# SIMICS\* OVERVIEW

## Contributor

#### **Daniel Aarno**

Software and Services Group, Intel Corporation Line break Jakob Engblom, Wind River

"A full-system simulator (FSS) like Simics is a model of a digital system that is complete enough to run the real target's software stack and fast enough to be useful for software developers."

"The main users of Simics are software and systems developers, and their main problem is how to develop complex systems involving both hardware and software."

This article provides an overview of Wind River Simics\*, a full-system simulation framework jointly developed by Intel and Wind River. Simics technology has been used to help develop complex software and hardware systems for more than two decades. This technical overview describes what Simics is, its main design goals and principles, and how it works. The article also describes the overall simulation landscape, and how Simics fits into the big picture.

## Introduction

A full-system simulator (FSS) like Simics<sup>[7]</sup> is a model of a digital system that is complete enough to run the real target's software stack and fast enough to be useful for software developers. The speed and full-system simulation capabilities of Simics differentiates it from most simulation tools provided by the electronic design automation (EDA) industry<sup>[8]</sup>, which are typically extremely accurate from a hardware perspective, but too slow to be practical for operating system (OS), application, or systems software.

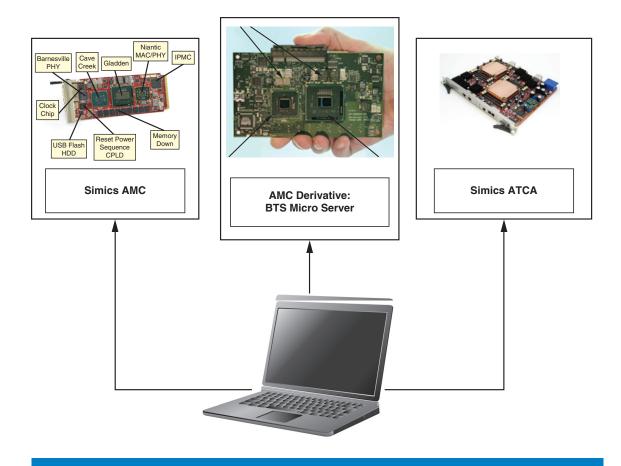

In an FSS, there are models of processors, memories, peripheral devices, networks, and so on, making up a model of the target machine. The key goal of the simulation is that as far as the software running on the target is concerned, it could just as well be running on physical hardware. Often this means that the simulation solution includes more than just the computer components. The simulation also integrates various simulators for the external environment that the computer system is operating in.

The main users of Simics are software and systems developers, and their main problem is how to develop complex systems involving both hardware and software. Virtual Machine Monitors (VMMs) like VMWare\* or Virtualbox\* also run complete software stacks—but for a runtime use case, not for the complete product lifecycle. In addition a VMM only simulates a generic, simplified hardware platform, whereas Simics can ensure binary compatibility with an actual real-world machine such as a specific Intel chipset (PCH) and processor variant.

## **Target Systems**

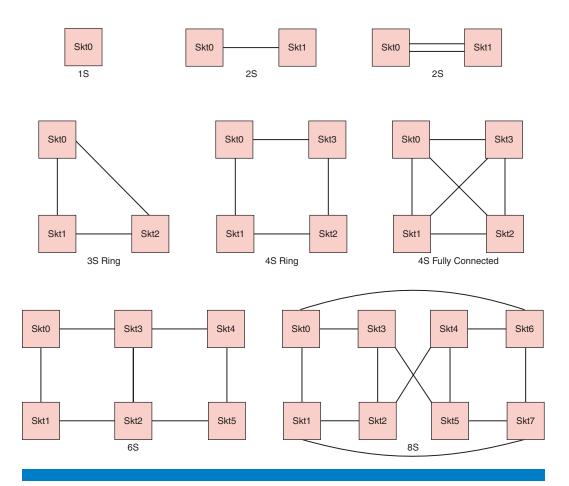

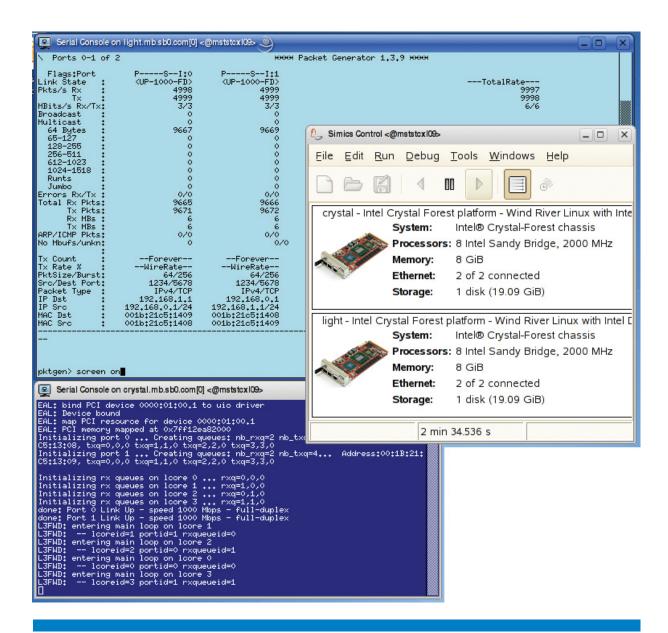

The target systems simulated with Simics range from single-processor aerospace boards to large shared-memory multiprocessor servers and rack-based telecommunications, data communications, and server systems containing thousands of processors across hundreds of boards. The systems are often heterogeneous, containing processors with different word-length, endianness, and clock frequency. For example, there can be 64-bit Intel Architecture (R)

processors running control software, alongside 8-bit microcontrollers managing a rack backplane, talking to data processing boards containing dozens of 32-bit VLIW DSPs. The target systems are typically built from standard commercial chips along with some custom FPGAs or ASICs.

Often, target systems are networked. There can be networks of distinct systems and networks internal to a system (such as VME, I<sup>2</sup>C, PCIe, and Ethernet-based rack backplanes). Multiple networks and multiple levels of networks are common.

Simulation runs can cover many hours or days of target time and involve multiple loads of software and reboots of all or part of the system. Even a simple task such as booting Linux and loading a small test program on an eight-processor SoC can take over 30 billion instructions. Profiling and instrumentation runs can take tens of billions of instructions.

Simics can be used to model future processors and chipsets well in advance of hardware availability. Such "early hardware" deployment of Simics allows BIOS, OS, and application software development to be performed long before even prototype silicon is available.

Simics is often used with models of hardware that are also available in silicon. Some models started life as early hardware models, and others have been created after the hardware was commercially available in order to directly support the main software and system development effort.

It is not uncommon for Simics to be used to model old hardware. Many embedded systems have lifespans covering decades, and development boards and tools tend to become exceedingly scarce over time. In such circumstances, Simics can provide an easily accessible, convenient, and available tool to keep up the maintenance of software for the systems.

#### **Simics Use Cases**

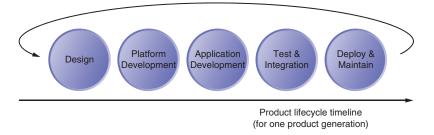

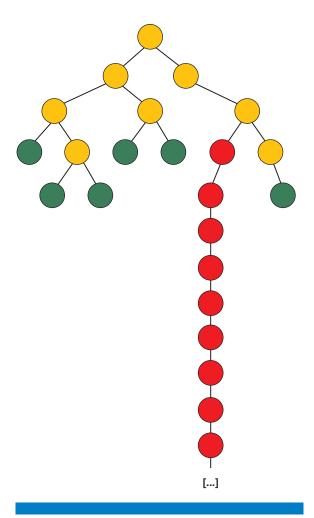

Full-system simulation can be applied during the complete product lifecycle as shown in Figure 1. It helps to define systems, by providing an executable model of the hardware interface and hardware setup. FSS supports hardware and software architecture work, and it validates that the hardware can be efficiently

Figure 1: Product lifecycle (Source: Wind River, 2013)

"Simulation runs can cover many hours or days of target time and involve multiple loads of software and reboots of all or part of the system."

"Simics can be used to model future processors and chipsets well in advance of hardware availability."

"The software development schedule can be decoupled from the availability of hardware..."

used from the software stack. FSS is used to develop system software, including debug and test. The software development schedule can be decoupled from the availability of hardware when using FSS and it improves software development productivity by providing a better environment than hardware.

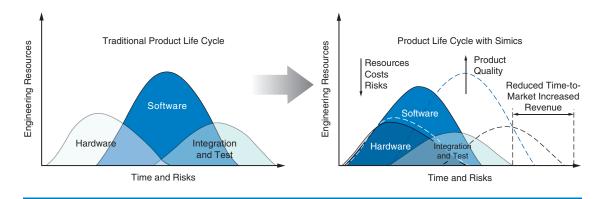

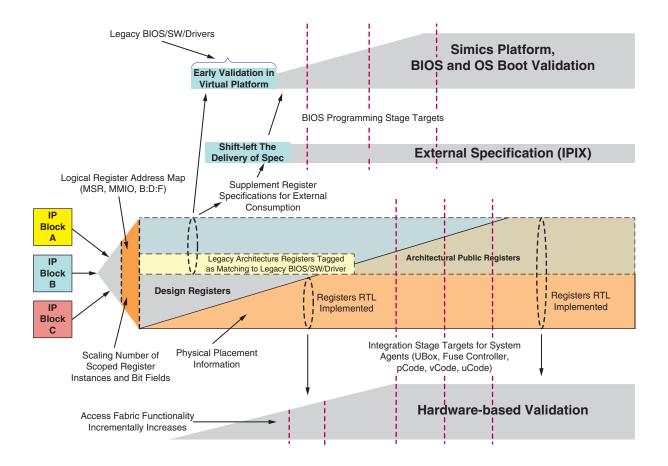

Figure 2 illustrates the concept of "shift-left", where software, drivers and BIOS development, integration, and test efforts are performed much earlier in the development process. This not only reduces products' time to market, it also reduces the cost of fixing defects when discovered earlier in the product lifecycle and increases product quality and customer satisfaction.

Figure 2: Shift-left of the product lifecycle (Source: Wind River, 2011)

The article "Using Virtual Platforms for BIOS Development and Validation" by Steve Carbonari describes the development of BIOS code on Simics models in advance of hardware availability, as well as how Simics is being used after silicon becomes available.

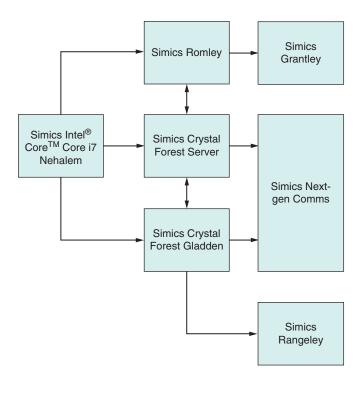

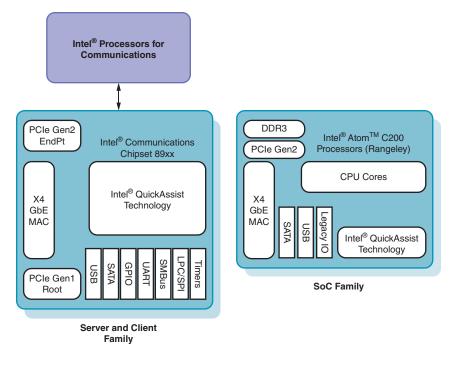

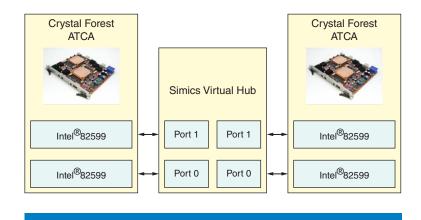

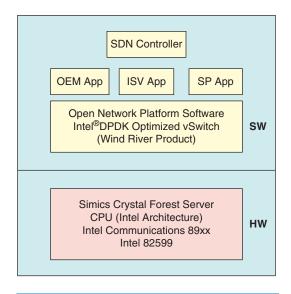

The article "Post-Silicon Impact: Simics Helps the Next Generation of Network Transformation and Migration to Software Defined Networks (SDNs)" by Tian Tian describes a high-level view of how Simics has been used for early hardware access for Intel communications chips, developing software stacks and drivers.

The article "Early Hardware Register Validation with Simics" by Alexey Veselyi and John Ayers describes a lower-level use case, where Simics is used to validate the register design of hardware very early in the design process.

A particular use of Simics is to change the simulation target during a simulation run in order to test software behavior. Simics can add and remove boards, bring new processors online, reconfigure network topologies, introduce faults in networks and hardware devices, and plug and unplug hot-pluggable hardware. The software will perceive these events like it would on physical hardware, allowing users to test and develop all aspects of the software stack, including automatic configuration, load balancing, fault detection, and fault recovery.

Simics can be used in tasks outside the immediate realm of development and engineering. For example, Simics has been used to demonstrate new products to

"Simics can add and remove boards, bring new processors online, reconfigure network topologies, introduce faults in networks and hardware devices, and plug and unplug hot-pluggable hardware."

prospective customers and to procurement agencies involved in large programs. Simics is also a training tool, both to train and educate users in general concepts (using Simics instead of hardware to make the training more efficient), and to train users of particular systems (typically developed using Simics to begin with).

As a system matures and the next generation begins development, Simics can be used to smoothly move from the current generation to the next generation. By setting up a model containing a mix of old and new hardware components (such as different generations of boards in a rack-based system), software can gradually be updated to match the next hardware generation. As part of this process, new boards can be tested in a system containing existing legacy boards. This is represented by the arrow back to the start in Figure 1.

"...Simics can be used to smoothly move from the current generation to the next generation."

# Important Features of Simics

The feature set of Simics has been developed and adjusted for more than twenty years in order to meet the needs of system developers (the first code in what was to become Simics was written in 1991). In this section, we describe the most important Simics features and why they were designed into the product.

#### Run Unmodified Real Software

A key design goal of Simics has always been to run the real software stack, as found on the target system. This includes the boot code or BIOS, operating system, drivers, and the applications and middleware running on top of that. Over the years, Simics has managed to run most types of software, including hypervisors with guest operating systems, small MMU-less embedded operating systems and bare-metal code, desktop and server operating systems like Windows\* and Linux\*, and real-time operating systems (RTOS) like VxWorks\*.

Running real unmodified software stacks has many benefits. Since Simics is primarily used for software development, running the actual software that is being developed makes eminent sense. The software is compiled using the same tools and compilers that are used with the hardware target, avoiding inconsistencies and deviations introduced by host compilation or other approximations or variant builds for simulation and quick tests.

Unmodified software also means unmodified build systems, and thus there is no need for users to set up special builds or build targets for creating software to run on Simics. There may be portions of the system where only machine code is available, such as proprietary libraries, drivers, or operating systems, and in such cases running the real binary code is the only way to get a complete software system running.

Using unmodified software also means that software can be managed and loaded in the same way as on a real system, making Simics useful for testing operations and maintenance of the target system.

The article "Using Virtual Platforms for BIOS Development and Validation" mentioned earlier describes how Simics is used to develop, test, and debug

"A key design goal of Simics has always been to run the real software stack,..."

"Simics is modular; each device model, processor, or other Simics model or feature is shipped in its own selfcontained dynamically loaded object file..."

low-level BIOS code, which is probably the most difficult type of software to run on a simulator.

The article "Using Simics in Education" by Robert Guenzel describes how Wind River makes use of the ability to run unmodified software to train users in topics like device driver development and network management.

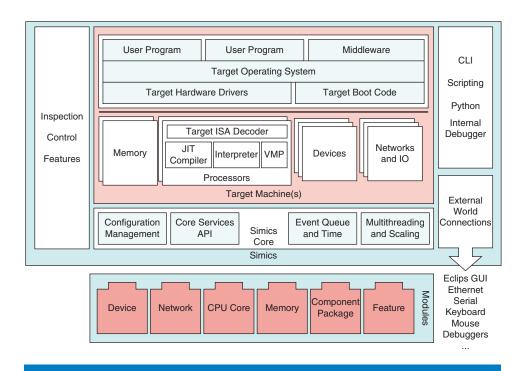

## Modularity

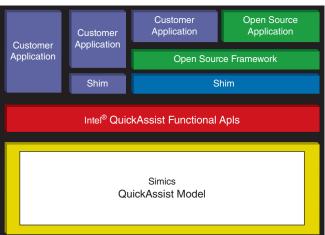

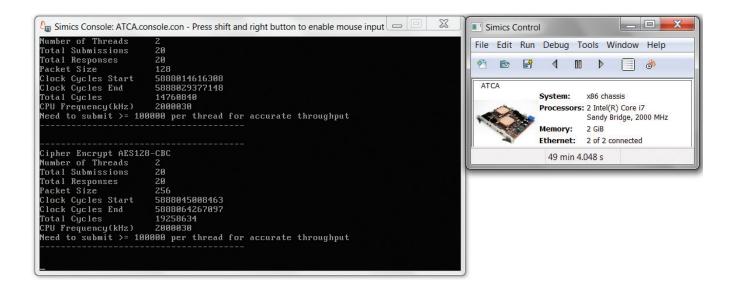

Simics is modular; each device model, processor, or other Simics model or feature is shipped in its own self-contained dynamically loaded object file (as shown at the bottom of Figure 3). This fine-grained structure makes it possible to supply the exact set of models and features needed for any specific user. The object file and its associated command files are referred to as a Simics module.

Figure 3: Simics architecture (Source: Wind River, 2011)

"Simics models can be distributed as binary-only modules,..."

Simics models can be distributed as binary-only modules, with no need to supply source code to the users. Binary distribution simplifies the installation for end users, as they do not have to compile any code or set up build environments. It also offers a level of protection for intellectual property when different companies exchange models. By obfuscating the names of hardware registers and limiting the amount of metadata included in the modules it is possible to safely distribute models of very sensitive future hardware designs to external users. It makes it possible to limit the information disclosure by the model to precisely that of the documentation provided, even if the model itself needs to contain undocumented and secret registers to make BIOS and low-level firmware code work correctly.

Simics modularity enables short rebuild times for large systems, as only the modules that are actually changed have to be recompiled. The rest of the simulation is unaffected, and each Simics module can be updated and upgraded independently.

A Simics model exposes an arbitrary set of interfaces to other models in other modules, and objects can call any model interface in any module. Interfaces are used both to model hardware communications paths and to implement other simulator functionality and information flows, such as getting the current cycle count of a processor or finding the address of a variable from the debug module. Unlike SystemC\*, an object can implement an interface multiple times using named ports and the bindings are not made at compile time. Some interfaces are unidirectional, but bidirectional interfaces (like network send and receive) are common and simply implemented as two complementary interfaces, one in each direction.

Simics uses the C-level ABI and host operating system dynamic loading facilities. The C++ ABI varies between compiler versions and compiler vendors, and is thus not usable in the interface between modules, even though C++ can be used internally in modules. The Simics framework provides bindings to write Simics modules using DML (see below), Python, C, C++, and SystemC, but users can actually use any language they like as long as they can link to C code. For example, a complete JVM has been integrated into Simics, running modules written in Java.[1]

#### **Scalability**

As discussed above, Simics target systems can potentially be very large. To efficiently simulate such large systems, Simics makes use of several techniques which are described in more detail in the section "Simics Performance Techniques." Scalability has been an important attribute of Simics since the very first commercial deployments, originally relying on distributed simulation<sup>[7]</sup>, and evolving into a multithreaded (and distributed) implementation.[8]

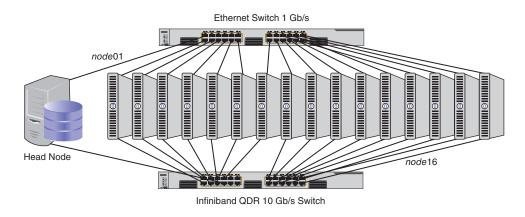

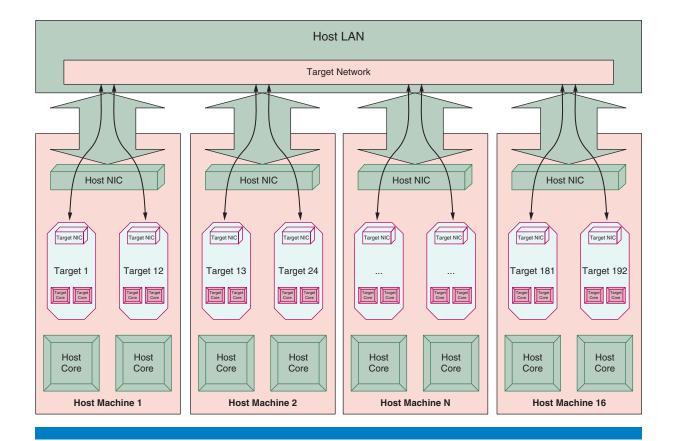

The article "Simics on Shared Computing Clusters: The Practical Experience of Integration and Scalability" by Grigory Rechistov describes a use case where Simics was scaled up and scaled out to run a simulation of more than one hundred Intel® Xeon® server boards, containing 1792 target processors.

#### **Multiple User Interfaces**

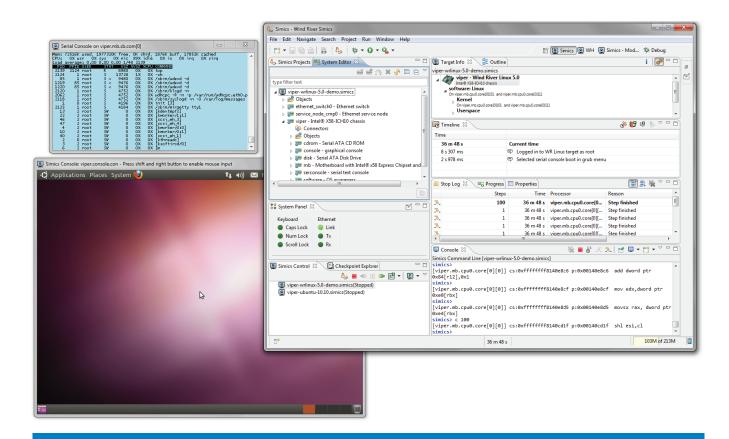

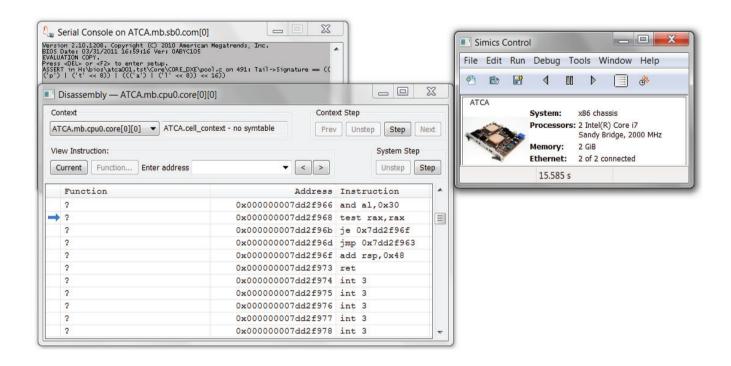

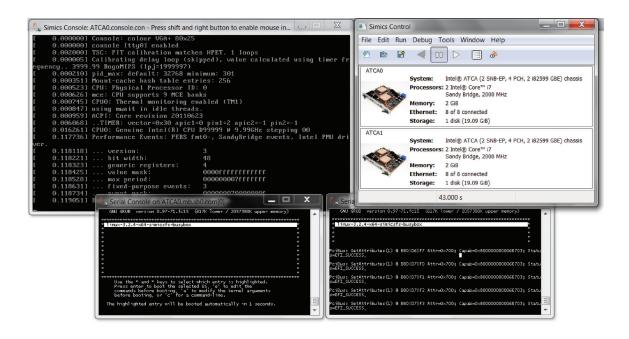

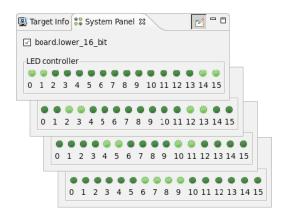

From the very beginning<sup>[7]</sup>, Simics was designed as an interactive tool that could also be used in automated batch runs. Given the wide range of users and usage scenarios, both command-line and GUI interfaces are needed. Today, the primary user interface for new users to Simics is the Eclipse-based GUI, but the command line is still there for more advanced tasks. Figure 4 shows a screenshot of the Simics 4.8 Eclipse GUI, running two simultaneous, but separate, simulation sessions (clockwise from top-left: simulated serial textterminal, Simics Eclipse GUI, simulated graphical console).

"...Simics was scaled up and scaled out to run a simulation of more than one hundred Intel® Xeon® server boards, containing 1792 target processors."

"From the very beginning<sup>[7]</sup>, Simics was designed as an interactive tool that could also be used in automated batch runs."

"...the Simics architecture separates the function of the target hardware system from the connections to the outside world."

"....Simics opens up a network connection from the virtual network inside of Simics to the host machine or other machines on the network."

Simics can also be run from a normal command-line shell, on both Linux and Windows hosts. This makes it possible to run Simics without invoking the Eclipse GUI and is useful when it comes to automating Simics runs from other tools. Simics behaves just like any other UNIX-style command-line application when needed.

As illustrated in Figure 3, the Simics architecture separates the function of the target hardware system from the connections to the outside world. The target consoles shown in Figure 4 are not part of the device models of the serial ports and graphics processor unit, but rather provided as generic functions by the Simics framework. This means that all consoles behave in the same way and provide support for command-line scripting, record and replay of inputs, and reverse execution.

In addition to the Simics console windows, a common way to interact with a Simics target machine is via a network connection. In this case, Simics opens up a network connection from the virtual network inside of Simics to the host machine or other machines on the network. This feature is known as "real network" in Simics. Users can then connect to Simics with the same tools as they would use to connect to a physical system on their network. Typically, ssh or telnet is used to get to a target command line, and remote debug protocols are used to control a target from an agent on the target machine.

Figure 4: Simics Eclipse GUI and target consoles (Source: Wind River, 2013)

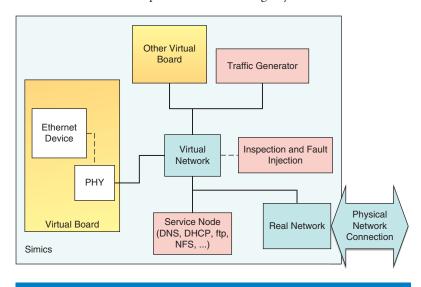

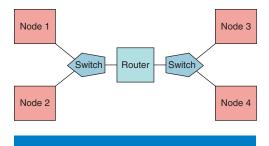

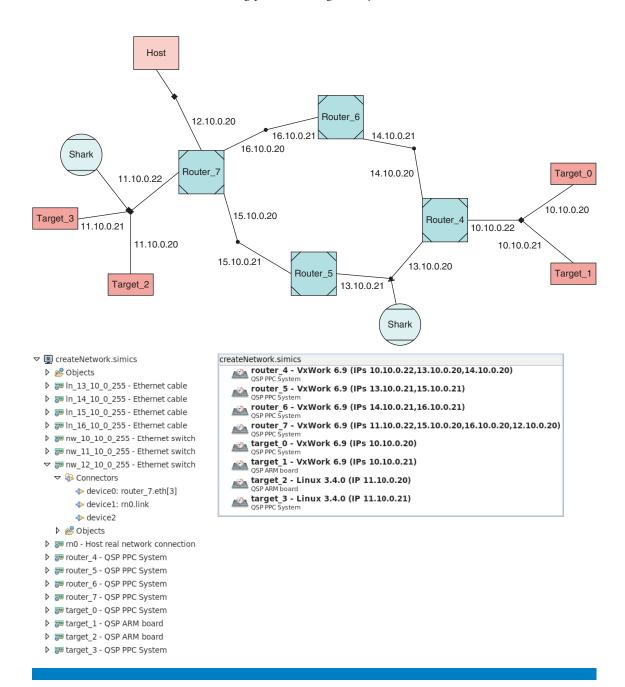

As illustrated in Figure 5, network connections from Simics to the outside world are accomplished indirectly. The target system is connected to a virtual network, and that virtual network can in turn add a connection to the real world. There can be other virtual target systems on the virtual network, and it is quite common to add features like traffic generators and inspection modules to a virtual network to inspect and affect the target system behavior.

Figure 5: Simics network simulation (Source: Wind River, 2013)

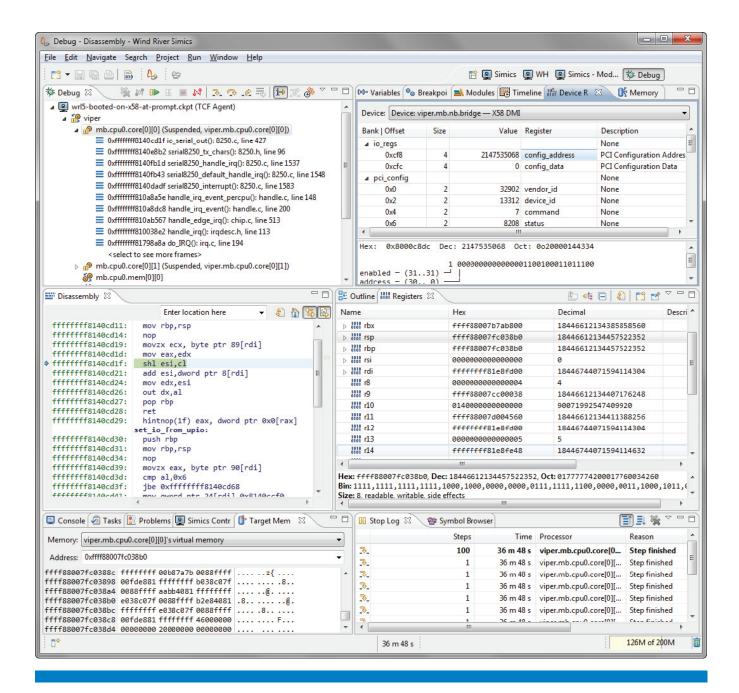

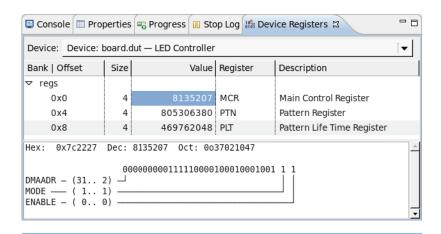

#### Visibility and Control

The Simics GUI, CLI, and the Simics API provide deep and rich access to the state of the target system and the simulation itself. It is easy to look inside any part of the system and check the state of hardware devices, processors, memories, and interconnects. Figure 6 shows an example of how the Simics GUI can be used to inspect various aspects of the state of the target system. The target software is executing inside a serial port driver in the Linux kernel, as can be seen from the stack trace in the upper left portion of the window. Other views display the device registers, memory contents, processor registers, and disassembly at the point of current execution.

As well as passively observing the state of the target system, Simics users can change it. This is used for fault injection or to quickly set up a system to make software run without necessarily having all boot code in place.

#### Scripting

Simics scripts work the same way in a Simics simulation started from Eclipse, in an interactive command-line session, and in an automated batch run on a remote compute server. Basic scripts are written in the Simics CLI command-line language, and for more complex tasks there is a full Python environment embedded in Simics. The Python engine has access to all parts of the simulated system and can interact with all Simics API calls. CLI and Python scripts can exchange data and

"It is easy to look inside any part of the system and check the state of hardware devices, processors, memories, and interconnects."

"...there is a full Python environment embedded in Simics."

Figure 6: Simics target system inspection (Source: Wind River, 2013)

"Users can create their own custom CLI commands..."

variables with each other, and it is common to find snippets of Python embedded inside of Simics scripts. Users can create their own custom CLI commands in order to automate or simplify common tasks peculiar to their system or environment.

A typical Simics scripting example is shown in Code 1. It is a script that opens a Simics checkpoint and then runs a command on the target. The parameters to the command are sent in as Simics CLI variables to this script, but are also provided with default values in case nothing is provided. The script branch at the end is a construct that lets script code run in parallel to the target system and react to events

in the simulation. This makes it very easy to automate and script systems containing many different parts where the global order of scripted events is unknown before the simulation starts. Separate scripts can be attached to the different parts.

```

## Parameters to run:

if not defined opmode { $opmode = "software byte" }

if not defined generations { $generations = 100 }

if not defined packet length { $packet length = 1000 }

if not defined packet count { $packet count = 1000 }

if not defined thread count { $thread count = 4 }

if not defined output_level { $output_level = 0 }

## Ensure stall mode to enable cache analysis

sim->cpu mode = stall

## Load existing checkpoint

$prev checkpoint file = (lookup-file "%script%") +

"/after-ca001-booted-and-setup.ckpt"

if not (file-exists $prev_checkpoint_file) {

interrupt-script "Please run ca001 script first

to establish the checkpoint!"

} else {

read-configuration (lookup-file $prev

checkpoint file)

$system = viper

$con = $system.console.con

# Script branch that will run the program and wait

for it to complete

# by watching the target serial console

$prog name = "/mnt/rule30 threaded.elf"

cmd = (%s %s %d %d %d %d %d \n" % [$prog name,

$opmode, $packet_count, $generations, $packet_

length, $output_level, $thread_count])

script-branch {

local $system = $system

local $con = $con

local $cmd = $cmd

local $prompt = "~]#"

add-session-comment "Starting run"

$con.input $cmd

$con.wait-for-string $prompt

add-session-comment "Run finished"

stop

Code 1. Example Simics Target Automation CLI Script

Source: Wind River, 2013

```

"Compared to configuring hardware lab setups for even small networks, Simics can save hours and days of setup time."

"The Simics debugger obviously supports reverse debugging,..."

"OS awareness provides the user with a full software perspective of the system,..."

Using Simics scripts, it is easy to automate and replicate the setup of even the most complex target systems. Multiple machines, boards, and networks can all be set up, configured, and reliably reproduced. Compared to configuring hardware lab setups for even small networks, Simics can save hours and days of setup time.

The article "Using Simics in Education" mentioned earlier describes how network topologies are automatically generated in order to support networking training, providing a typical example of the power of Simics scripting to automate system setups.

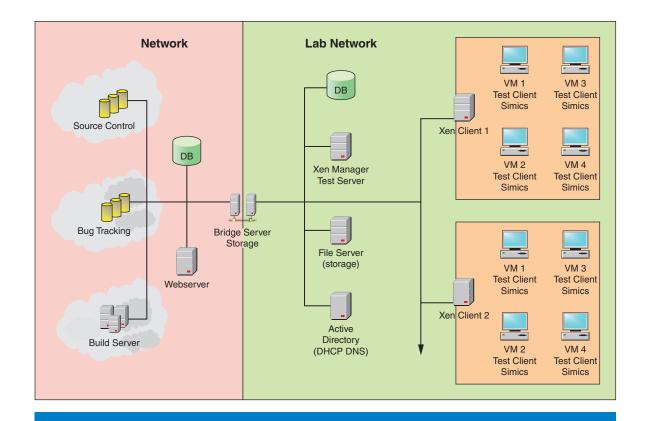

Another use-case enabled by automation is testing of code as it is being built or checked into version control. With Simics, it is quite easy to launch an actual target machine (for any target architecture), load the software, and test it. Physical hardware would be much harder to invoke on-demand and automatically in this fashion.

"Using Virtual Platforms for BIOS Development and Validation" mentioned earlier describes how BIOS code is tested on check-in, both before and after the availability of silicon.

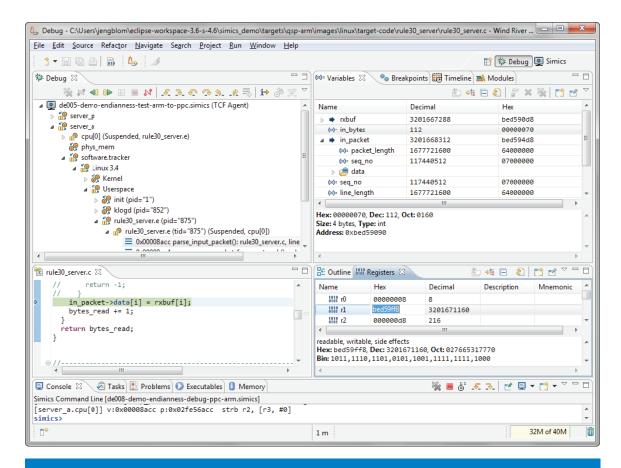

## OS Awareness and Debugging

Simics includes a very powerful full-system debugger, based on Eclipse CDT and some Wind River extensions. The debugger functionality is equally accessible from the Simics command line, providing the ability to automate debug tasks and to control the debugger from the CLI while looking at the state of the system in the GUI.

The Simics debugger obviously supports reverse debugging, as well as user operations that arbitrarily change the target's state and time. Simics has the ability to trace or put breakpoints on aspects of the target that are inaccessible on the hardware, such as hardware interrupts, processor exceptions, writes to control registers, device accesses, arbitrary memory accesses, software task switches, and log messages from device models. In Simics it is possible to single-step interrupt handling code and to stop an entire system, consisting of multiple networked machines, synchronously.

As Simics models the actual hardware and runs the OS code just like the physical hardware would, it does not directly know anything about the OS. Indeed, it is not necessary to run an OS on a Simics model, "bare-metal" code is commonly used for low-level tasks. Thus, for Simics to be able to provide advanced features based on the OS running on the target a feature known as OS awareness is necessary. OS awareness provides the user with a full software perspective of the system, in addition to the hardware perspective. OS awareness allows Simics investigate to the state of the target system and resolve the current set of executing threads and processes. The OS awareness module for a particular OS knows the layout and structure of things like process descriptor tables and run queues, and can provide the debugger with information about the currently running processes and threads. OS awareness lets the Simics debugger, scripts, and extensions act when programs and processes are started, terminated, or switched in and out.

The debugger leverages OS awareness to allow debugging of individual applications and threads, as well as stepping up and down through the software stack layers. Symbolic debug information can be attached to processors for bare-metal debug and to software stack contexts (like a kernel or user application) for debugging only a certain part of the software system.

The Simics debugger is a full-system debugger, meaning that it connects to the entire target system and not just a single processor or board. In Figure 7, we see two target machines inside a single debug session (server\_p and server\_a),

"The debugger leverages OS awareness to allow debugging of individual applications and threads, as well as stepping up and down through the software stack layers."

Figure 7: Simics debugger (Source: Wind River, 2013)

as well as OS awareness digging down to a certain thread inside the program called "rule30\_server.e" and doing source-level debug on this particular program in the context of the overall system.

#### Checkpointing

Simics has been designed from the ground up to support checkpointing of the simulation state. This gives Simics the ability to save the complete state of a simulation to disk and later bring the saved state back and continue the simulation without any logical interruption from the perspective of the hardware model and the target software.

"Simics has been designed from the ground up to support checkpointing of the simulation state."

"Checkpoints contain the state of both the hardware and the software..."

Checkpoints contain the state of both the hardware and the software (which is implicit in the hardware state as it is described by the contents of memory, disks, CPU registers, and device registers). Based on our experience, Simics checkpoints are portable across time and space, and let users do things like the following:

- Restore the simulation state from a previous run for the same user on the same machine as the checkpoints were taken. This helps an individual user work more efficiently.

- Restore on a different host machine. This means that checkpoints can be shared between users, enabling all kinds of collaboration.

- Restore into an updated version of the same simulation model. This makes it possible to use checkpoints taken with older versions of a model, making them portable across time.

- Restore into a completely different simulation model that uses the same architectural state. For example, a detailed clock-cycle driven model initialized from a fast Simics run.

- Replay a particular sequence of inputs captured in one simulation session into a second simulation session.

Checkpointing can be used to support workflow optimization, such as a "nightly boot" setup where target system configurations are booted as part of a nightly build, and checkpoints saved. During the workday, software developers simply pick up checkpoints of the relevant target states, with no need to boot the target machines themselves.

Another important use of checkpointing is to package bugs and communicate them between testing and engineering, between companies, and across the world. Simics checkpoints make the reproduction of the bug and the environment needed to reproduce the bug trivial. [2]

Simics checkpoints can contain an embedded history of asynchronous inputs. This makes it possible to communicate a slice of time, and not just an instantaneous state of the target machine. Alternatively, a checkpoint of a single point in time can be used along with a script that drives the simulation in a deterministic way to achieve the same effect.

# Repeatability and Reversibility

Simics has been designed from the bottom up to be a repeatable and deterministic simulator, with the exact same simulation semantics regardless of the host machine. As long as asynchronous input to the simulator is being recorded, any simulation run can be repeated precisely on any host at any time. Note that determinism does not mean that the simulation always runs the same target software in the same way. If the timing of any input, or any part of the initial state changes, the simulation will execute differently.

Determinism does not prevent a user from exploring variations in target software behavior. Rather, the user remains in control and can repeat any simulation run where the variations triggered some interesting behavior.

"...package bugs and communicate them between testing and engineering, between companies, and across the world."

Based on repeatability, Simics also implements reverse execution and reverse debugging, where the user can go back into the history of the system execution. Reverse execution was incorporated in Simics 3.0 and launched in March of 2005, which makes it the first usable reverse execution implementation. This is a powerful tool for software debugging, especially for intermittent and timingdependent bugs, which are difficult to reproduce on hardware using classic iterative debugging. Note that Simics reverse execution applies to a complete target system, including multiple processors, boards, and operating-system instances. Network traffic, hardware accesses, and everything else going on in the system is reversed, not just a single user-level process as is targeted by most other reverse execution approaches such as gdb.[3]

A key enabler for determinism, checkpointing, and reverse execution is that Simics simulation models do not normally use resources outside the simulator; notice that the target machine is internal to Simics in Figure 3 and how the network is isolated from the model in Figure 5. Hardware models live in a completely virtual world and do not open files on the host or drive user interaction directly. All external interaction is handled by the Simics kernel and special infrastructure modules for text consoles, graphical consoles, and network links. In the case that the outside world needs to be connected to a model, Simics provides a recorder mechanism that can reliably replay asynchronous input under reverse execution.

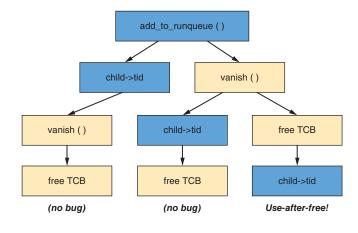

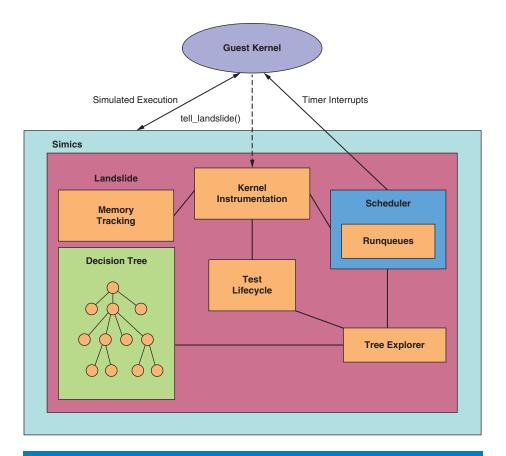

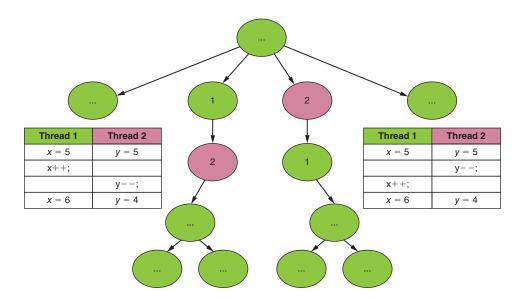

The article "Landslide: A Simics Extension for Dynamic Testing of Kernel Concurrency Errors," by Ben Blum, David A. Eckhardt, and Garth Gibson, provides an example of a creative use of reverse execution. It is employed to implement a backtracking search through the execution space of a concurrent software stack.

#### **Dynamic Configuration and Reconfiguration**

A Simics simulation can be reconfigured and extended at any point during a simulation. New modules can be loaded and new hardware models and Simics extensions added. All connections can be changed, and simulation models deleted or disconnected from the running system.

Such changes are done from scripts, the Simics command-line, and the System Editor in Eclipse at will. This dynamic nature of a system is necessary to support system-level development work and to support the dynamic nature of the target systems discussed in the introduction.

# **Extensibility and Programmability**

Simics is an extensible and programmable system. Any Simics user is able to build not just new device models and system configurations, but also arbitrary Simics extensions. With the Extension Builder product, users have access to the complete Simics API and can basically implement any functionality they want to. New functionality often starts out as scripts, but over time it migrates into custom Simics modules in order to make the setup more robust and to achieve higher performance.

"...Simics reverse execution applies to a complete target system, including multiple processors, boards, and operating-system instances."

"Any Simics user is able to build not just new device models and system configurations, but also arbitrary Simics extensions."

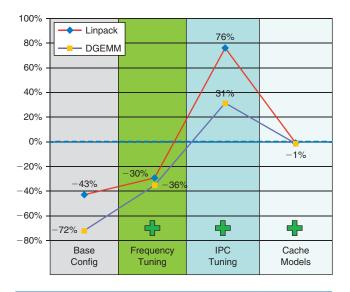

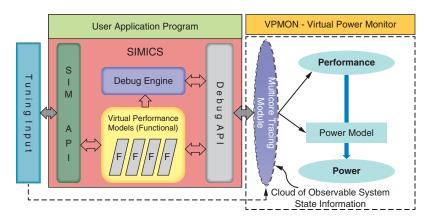

The article "Software Power and Performance Correlation on Simics" by Parth Malani and Mangesh Tamhankar describes an implementation of a power estimation tool inside of Simics, quite radically extending the kinds of data that can be collected from Simics.

The article "Sim-O/C: An Observable and Controllable Testing Framework for Elusive Faults," by Tingting Yu, Witawas Srisa-an, and Gregg Rothermel, and the article "Landslide: A Simics Extension for Dynamic Testing of Kernel Concurrency Errors," mentioned earlier both provide examples of how custom Simics modules can be used to build powerful software verification tools on top of Simics.

## **External World Connectivity**

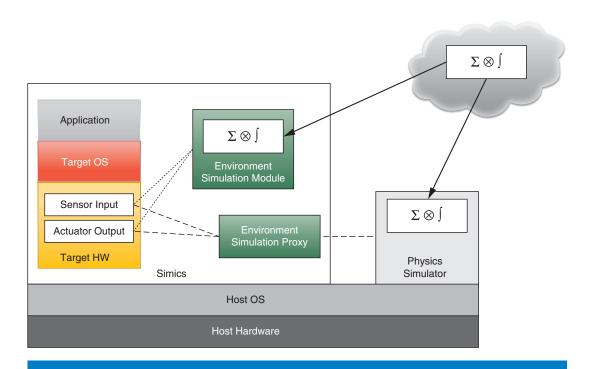

A simulator used for system development and software development often needs to include more than just the computer system and its software. In some way, the outside world needs to be introduced into the system.

The most basic connections are the serial and graphics consoles provided with Simics to allow a user to interact with the simulated computer system. It is also quite common to connect Simics simulated machines to the real world via Ethernet networks and serial ports, using various real-network systems to bridge between the physical world and the virtual system (as illustrated in Figure 5). In this way, Simics target systems have been used in hardware-in-the-loop simulations.

Today, it is very common to use simulation of the physical world during the design of products like vehicles, space crafts, and engines. Such environment simulators can be integrated with Simics, creating holistic models that encompass all aspects of the target system. Essentially, hardware-in-the-loop is replaced by simulation-in-the-loop, making it possible for any developer to have a complete cyber-physical system on their desk for software testing and debugging.

Figure 8 shows how such a setup is achieved. On the Simics computer side, there need to be models of the actual devices the computer uses to sense and control its environment. Then, the environment model is either run inside of Simics, or (more commonly) in a separate process communicating with a proxy module in Simics over a network socket or other inter process communication mechanism.

# **Simics Performance Techniques**

Simics is designed from the ground up to be a fast simulator in the tradition of software-oriented simulators going back to the 1960s. [4] The key design goal is that it is better to run a whole software stack with a low level of timing fidelity, rather than run a very small piece of software with a high level of timing fidelity. For most software, detailed hardware timing simply does not matter much, and Simics takes advantage of this to create a very fast simulator.

#### Transaction-Level Modeling

Simics is built on the ideas that are now generally known as transactionlevel modeling. All memory accesses in Simics are performed as synchronous transactions that pass through the entire hierarchy of memory maps, call a device function, and return immediately.

"...making it possible for any developer to have a complete cyberphysical system on their desk for software testing and debugging."

"For most software, detailed hardware timing simply does not matter much, and Simics takes advantage of this to create a very fast simulator."

Figure 8: Simics and physics simulators (Source: Wind River, 2013)

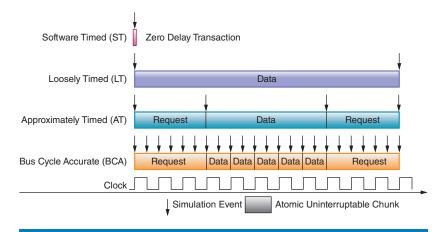

The Simics memory model is similar to the SystemC TLM 2.0 loosely timed (LT) model<sup>[5]</sup> in that a memory access is a blocking call. However, the Simics model is a special case of the LT model with a zero time delay; this is sometimes referred to as software-timed (ST) or programmer's view (PV). The different common timing models are illustrated in Figure 9.

Figure 9: Simics TLM abstraction (Source: Intel Corporation, 2013)

"...detailed SystemC models can be integrated into Simics, creating a hybrid setup with a good balance between performance and simulation detail."

"This allows Simics to reach speeds in excess of 1000 MIPS..."

Often, immediate completion of an operation when a device register access occurs is sufficient for modeling a device. When hardware units need to raise completion interrupts or change status registers after a significant time, events are used. The device model posts an event for some point in the future and then completes the current operation. When the time for the event comes, the device model gets a callback and it can set status bits, trigger interrupts, and complete work that should not be observed by the software until that time. Simics devices do not use threads to model time, only events. This principle is applied to all types of communication in Simics, including networks, serial lines, and buses connecting hardware units. It opens up for a host of optimizations in the core simulation system.

Still, it is possible to connect more detailed models into Simics. Typically, most of the system runs at the standard Simics level of abstraction in order to maximize speed, with a few units replaced with detailed models driven by the software running on the fast Simics models.

The article "Simics-SystemC\* Integration" by Asad Khan and Chris Wolf describes how detailed SystemC models can be integrated into Simics, creating a hybrid setup with a good balance between performance and simulation detail. It is also common to connect Simics with hardware emulators.

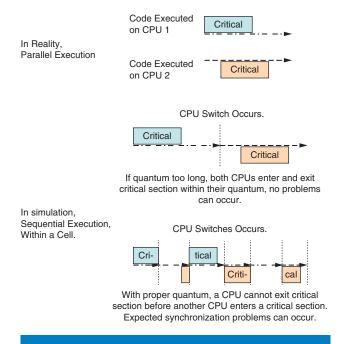

## Temporal Decoupling

Temporal decoupling is a standard technique for improving the performance of a simulation containing multiple concurrent units. Rather than switching between the units at each step of the simulation, such as a clock cycle, each unit is allowed to run for a certain amount of virtual time, its time quantum, before switching to the next unit. Temporal decoupling has been in use for at least forty years in the area of computer simulations<sup>[5]</sup> and is a crucial part of all fast simulators today<sup>[6]</sup>. Experience shows that using a fairly large time quantum is critical to achieving really high simulation speeds. In our experience, performance typically increases by a factor of 100 from a time quantum of 10 cycles to a time quantum of 100,000 cycles. As far as the software is concerned, time quanta below 100,000 cycles tend to be unnoticeable.

#### **Fast Processor Simulation**

Simics CPU models employ JIT simulation techniques where the target CPU code is translated into code for the host CPU. This allows Simics to reach speeds in excess of 1000 MIPS when simulating compute bound code on nonnative instruction sets such as a Power Architecture target on an Intel® architecture host.

For Intel architecture targets, Simics also takes advantage of the Intel® Virtualization Technology (Intel® VT) found in Intel processors to run the target code directly on the host. This makes it possible to achieve performance close to native speeds.

Another important processor simulation technology is hyper-simulation, where the processor model skips through idle time in a single simulation step, rather

than going through it cycle by cycle. For example, if an Intel architecture processor executes the HALT instruction, it will not do anything until the next interrupt. Since Simics knows when the interrupt will happen, time is advanced immediately. This is enabled by the architectural isolation of targets from their environment, as illustrated in Figure 3. Simics hyper-simulates defined idle instructions, but can also automatically detect loops that do nothing except wait for an event and immediately skip forward to the loop exit condition. This means that hyper-simulation applies to many operating system idle loops, even when such loops do not make use of power save or idle instructions.

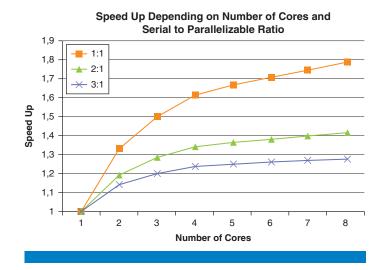

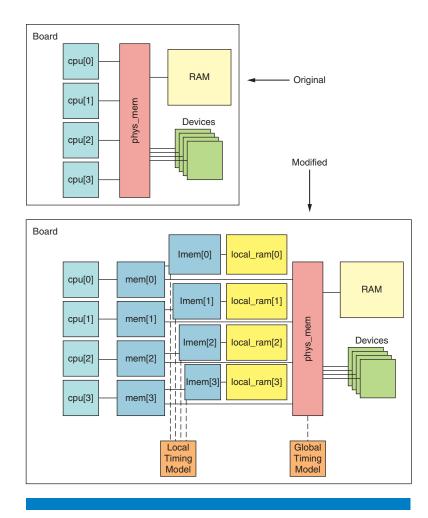

#### **Multithreaded Simulation**

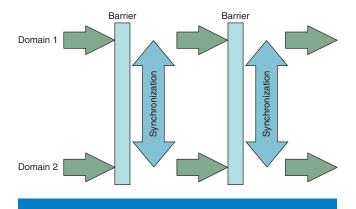

Simics makes use of multiple host processor cores to simulate the target system. When running in *multithreaded* mode, Simics still implements precisely the same target semantics and behavior as when running single threaded. This means that the simulation behavior is independent of the host, and that simulation repeatability is maintained as checkpoints and setups are communicated between Simics users.

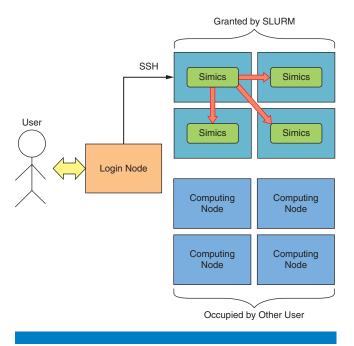

When the processor power (or memory) of a single host is insufficient to run a large system, Simics can also use distributed simulation. In such a setup, multiple Simics processes running on different hosts are connected into a single coherent and time-synchronized simulation system. Multithreading lets Simics take advantage of scale-up of individual hosts, and distribution takes advantage of scale-out as more simulation hosts are added. See the article by Rechistov for an example of scaling up and scaling out Simics to run a very large target system.

# **System Modeling**

Getting a model in place for a relevant target system is a prerequisite to using Simics. Without some virtual hardware to run on, software will not be particularly interesting.

#### **Using Existing Models**

The simplest way to get a model is to use one that already exists. This is a fairly common case in practice, since Intel and Wind River have a substantial library of existing models that can be used. For example, Intel has created models of quite a few modern Intel hardware platforms, and such platform models can be used with very little work. Over time, platform models (typically of reference boards) tend to be customized to become models of the actual boards used in a particular system.

For other users, a standard system might be sufficient. Simics ships with Quick Start Platforms (QSP), which provide a simple idealized multicore system that runs Wind River Linux and VxWorks by using customized BSPs. The QSP provides serial ports, Ethernet ports, timers, and disks. The QSP will not run the same bootrom and OS image as a real board, but it will in general run userlevel application binaries compiled for the real system. In this way, they provide a system that gets a user started quickly and that is entirely sufficient for using Simics features to debug, test, and analyze software applications.

"Simics makes use of multiple host processor cores to simulate the target system."

"...Intel and Wind River have a substantial library of existing models that can be used."

"...Simics provides the tools necessary to quickly and efficiently develop new models that can be easily integrated into existing targets."

"DML is based on the view that modeling is programming,..."

## **Device Modeling**

If a model does not exist, Simics provides the tools necessary to quickly and efficiently develop new models that can be easily integrated into existing targets. The core of building models of new hardware in Simics is the modeling of the device found in the new hardware. As mentioned above, Simics provides a C API and ABI meaning that models written in almost any language can be integrated into Simics. However, Simics also provides its own domain specific language, the Device Modeling Language (DML), which is specifically developed to allow rapid development of robust device models for Simics. Besides DML, the other most commonly used languages for creating device models are C, C++ (including SystemC), and Python.

DML essentially wraps snippets of C code inside a language designed to make it easy to express device register maps and other common hardware modeling constructs. DML is based on the view that *modeling is programming*, and tries to make the code required to describe a device model as short and concise as possible.

Key features supported by DML include expressing register maps, bit fields in registers, bit-endianness, byte-endianness, multiple register banks, simulator kernel calls such as event posting, and the connections between cooperating device models. *Templates*, not to be confused with C++ templates, are used to provide reuse for repeated patterns of code. DML cuts down on repetitive coding and makes device model code easier to write and maintain. DML can also be used to wrap existing C and C++ models of algorithms and core hardware functionality into a register map and Simics model, enabling their use inside of a Simics virtual platform. DML separates declarations and definitions, allowing reuse of artifacts from the hardware design by automatically converting register descriptions to DML declarations.

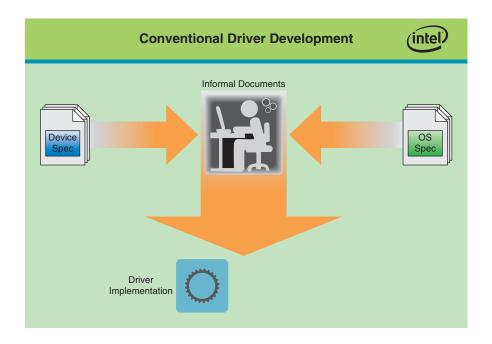

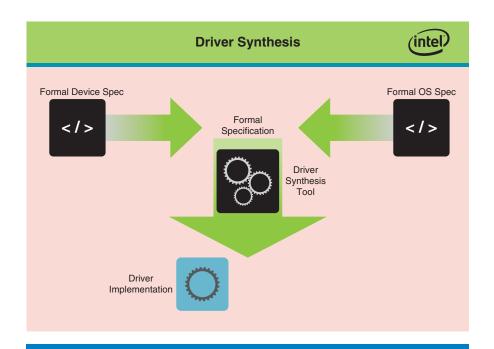

The article "Device Driver Synthesis" by Mona Vij et al. describes a creative use of the device models created for Simics. They use DML models of hardware created as part of the hardware design process as an input to a tool that creates device drivers.

The article "Using Simics in Education" mentioned earlier contains an example of using DML to create a device for the purpose of training in device driver development.

No matter how device models are programmed, the recommended methodology in Simics is to build functional tests that test a device in isolation before integrating it into a system. For this purpose, a test framework written in Python is provided, along with an Eclipse GUI to make running and inspecting tests a natural part of the development flow.

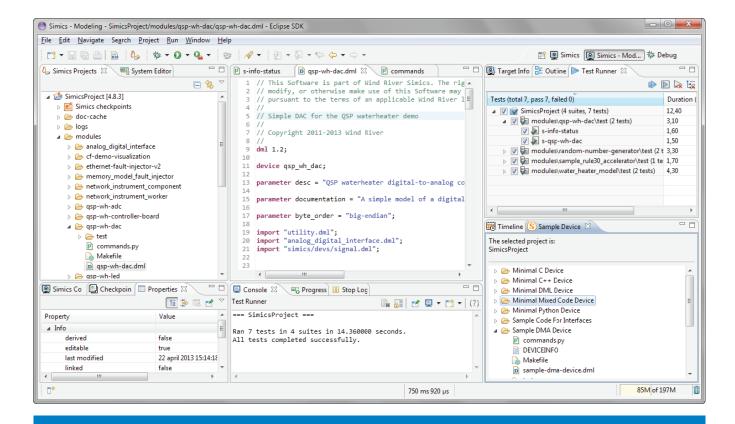

Figure 11 shows some of the Eclipse views provided by Simics to aid modeling. We can see the Test Runner in the upper right-hand corner, and

Figure 11: Simics modeling in eclipse (Source: Wind River, 2013)

the Sample Device browser below it. The Eclipse "New Sample Device" wizard creates new devices, and other modules, based on the examples provided with Simics. The Sample Device view lets you look at the example code without necessarily creating a new device model in your own workspace. This is quite convenient when borrowing functionality from an example.

#### **Component System**

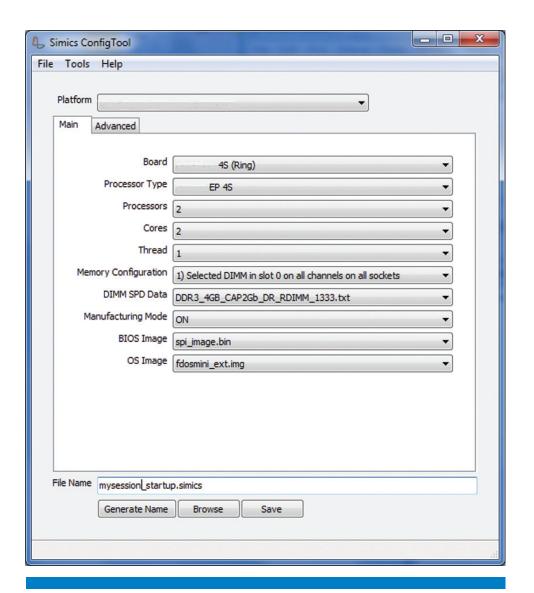

To aid configuration and management of a simulation setup, Simics has the concept of components. Components describe the aggregations of models that make up the units of a system, such as disks, SoC, platform controller hubs, memory DIMMs, PCI Express\* cards, Ethernet switches, and similar familiar units. They carry significant metadata and provide a natural map of a system.

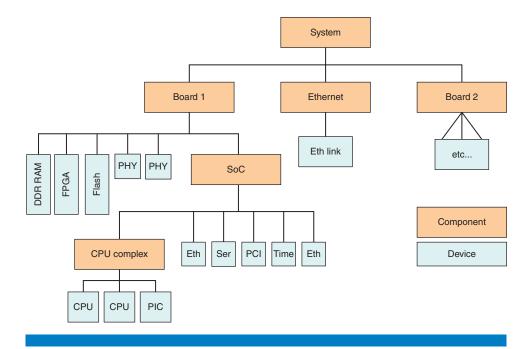

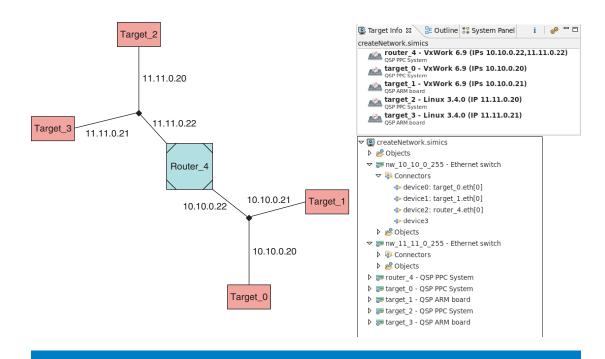

Figure 12 shows a stylized example of a component hierarchy, where a system is built from two boards connected by an Ethernet network. At each level of the hierarchy, device models can be present, as well as components. The component system provides both structure to the models and a hierarchical namespace for the running simulation, making it easy to reuse components and devices without any risk of names clashing.

"The component system provides both structure to the models and a hierarchical namespace for the running simulation,..."

Figure 12: Simics component system (Source: Wind River, 2013)

Components encapsulate the details of connections between parts of the system, creating abstractions like DDR memory slots, PCIe slots, and Ethernet ports. Components can be used to change the simulation configuration both during initial setup and at runtime.

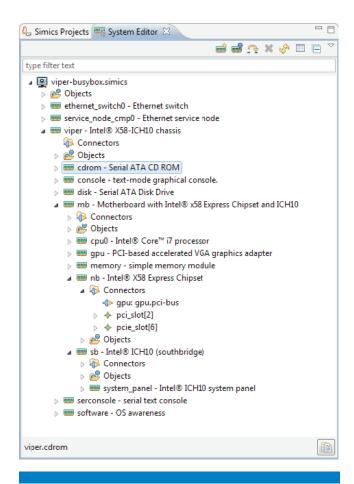

Figure 13 shows an example of the system editor view in Eclipse with an instantiated real component hierarchy from a simple target called "Viper." The Viper target has a model of an Intel® Core™ i7 processor and an Intel® X58 chipset, and it can be seen how it is hierarchically constructed from components reflecting the logical hierarchy of the physical hardware.

Components usually have parameters like the number of processor cores to use in a processor, the size of memories, the clock frequency of a core, or the MAC addresses of an Ethernet controller. Components provide the standard way to create Simics simulation setups, and a normal Simics setup script simply creates a number of components and connects them together.

"Components usually have parameters like the number of processor cores to use in a processor, the size of memories, the clock frequency of a core, or the MAC addresses of an Ethernet controller."

## **Summary**

In this introductory article, we have presented the Simics technology along with some of its use cases and features. The following articles in this issue of the Intel Technology Journal will describe particular ways in which Simics has been used at Intel, Wind River, and in academia.

Figure 13: Example of a component hierarchy (Source: Wind River, 2013)

#### References

- Introspection of a java virtual machine under simulation, Tech. Rep. SMLI TR-2006-159, Sun Labs 2006.

- Engblom, Jakob: Transporting Bugs with Checkpoints, in [2] System, Software, SoC and Silicon Debug Conference (S4D 2010), Southampton, UK, September 15-16, 2010.

- Engblom, Jakob: A review of reverse debugging, in System, Software, SoC and Silicon Debug Conference (S4D 2012), Vienna, Austria, September 19-20, 2012.

- [4]Kazuhiro Fuchi, Hozumi Tanaka, Yuriko Manago, and Toshitsugu Yuba. 1969. A program simulator by partial interpretation. In Proceedings of the second symposium on Operating systems principles (SOSP '69). ACM, New York, NY, USA, 97-104. DOI=10.1145/961053.961092 http://doi.acm.org/ 10.1145/961053.961092

- IEEE Standard for Standard SystemC Language Reference [5] Manual, IEEE Std 1666, 2011.

- [6] Cornet, J., Maraninchi, F., Maillet-Contoz, L. 2008. "A method for the efficient development of timed and untimed transactionlevel models of systems-on-chip." DATE '08: Proceedings of the conference on Design, automation and test in Europe, pp. 9-14. doi http://doi.acm.org/10.1145/1403375.1403381

- [7] Magnusson, P., Christensson, M., Eskilson, J., Forsgren, D., Hallberg, G., Hogberg, J., Larsson, F., Moestedt, A., Werner, B.: Simics: A full system simulation platform. Computer 35(2), 50–58 (2002).

- [8] Jakob Engblom, Daniel Aarno, and Bengt Werner, 2010. "Full-System Simulation from Embedded to High-Performance Systems". Processor and System-on-Chip Simulation, Rainer Leupers and Olivier Temam (ed), Springer New York Dordrecht Heidelberg London, ISBN 978-1-4419-6174-7, DOI 10.1007/978-1-4419-6175-4.

## **Author Biographies**

Daniel Aarno is an engineering manager in Intel's Software and Services Group where he leads a team working on the Simics full system simulation product. Daniel joined Intel in 2010 through the acquisition of Virtutech.

Daniel holds a master's degree in electrical engineering and a licentiate's degree in computer science. Prior to joining the Simics team at Virtutech, Daniel was doing research at the Centre for Autonomous Systems at the Royal Institute of Technology, focusing on human-machine collaboration. During this time he took part of the PACO+ consortium within the 6th framework for research in the EU.

Jakob Engblom is a technical marketing manager for tools at Wind River, with an emphasis on product management for Simics as a commercial product (for end users outside of Intel). He has been working with Simics since 2002, when he joined Virtutech right after getting his PhD in Computer Systems from Uppsala University, Sweden. He also holds a master's degree in computer science from Uppsala University. Over the years, he has worked with Simics in a variety of roles, including outbound marketing, inbound marketing, sales and field engineering, managing the academic program, and product management. He has written and presented more than 100 articles, papers, and talks on a variety of embedded systems topics since 1997. Currently, his main interests are in computer simulation, general simulation, programming, and debugging. He has a personal blog at http://jakob.engbloms.se, and blogs regularly on the Wind River tools blog at http://blogs.windriver.com/tools/.

# USING VIRTUAL PLATFORMS FOR BIOS DEVELOPMENT AND VALIDATION

## Contributor

#### **Steve Carbonari**

Intel Corporation

"BIOS demands additional functionality and depth from software simulation."

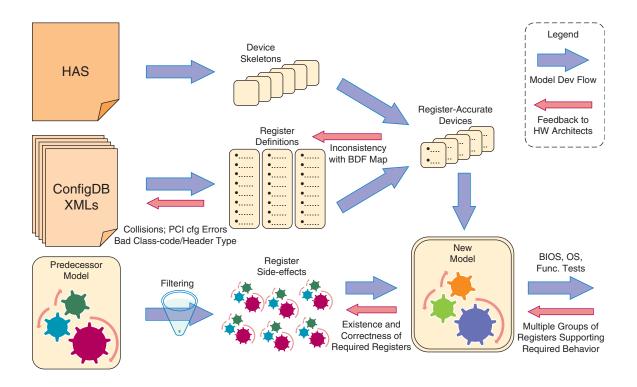

Creating a simulation environment for the purpose of BIOS debugging and validation requires in-depth simulation models. A separation of initialization versus runtime models is required to optimize performance, improve simulation initialization accuracy, and the debugging environment. The usage model for BIOS debugging and validation can be broken up into two categories: pre-silicon (before initial hardware is available) and post-silicon (after initial hardware is available). Specific debugging features are required to debug BIOS programs due to the large volume of interaction with the system hardware, its impact to the simulation environment, and a desire to replicate the power-on environment interfaces. Specific attention should be given to signaling a software programming error as soon as possible. In addition, specific simulation techniques need to be applied for BIOS memory reference code support. Lastly, using the simulation for validation requires configuration flexibility and fault injection to fully validate all paths within the BIOS being validated. This article describes the high level concepts and additional depth of modeling used to approach debugging and validating BIOS with simulation tools. Although the context of the article is BIOS development and validation, the concepts can be applied to simulation for any firmware project.

## Introduction

BIOS (Basic Input/Output System) refers to the software that runs after initial power is applied to the computer platform. BIOS' primary function is to initialize all hardware components to enable the computer platform to run higher level software (such as an operating system). Developing, debugging, and validating BIOS using software simulation demands additional functionality and simulation depth. Particular attention needs to be given to signaling errors at the time of register write, platform configurability, and mechanisms for fault injection. This article describes the basics of separating simulation runtime versus initialization, pre-silicon versus post-silicon usage models, development and debugging in the context of BIOS (specifically memory and processor interconnect initialization code), and BIOS validation requirements.

#### **Initialization versus Runtime**

To fully understand the demands that BIOS places on a simulation tool, an understanding of the differences between hardware initialization and runtime environments must be understood. When hardware is first powered on, only the minimal amount of components have power. Low-level firmware initializes the minimal amount of hardware components to enable BIOS to execute.

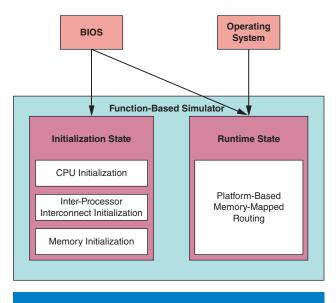

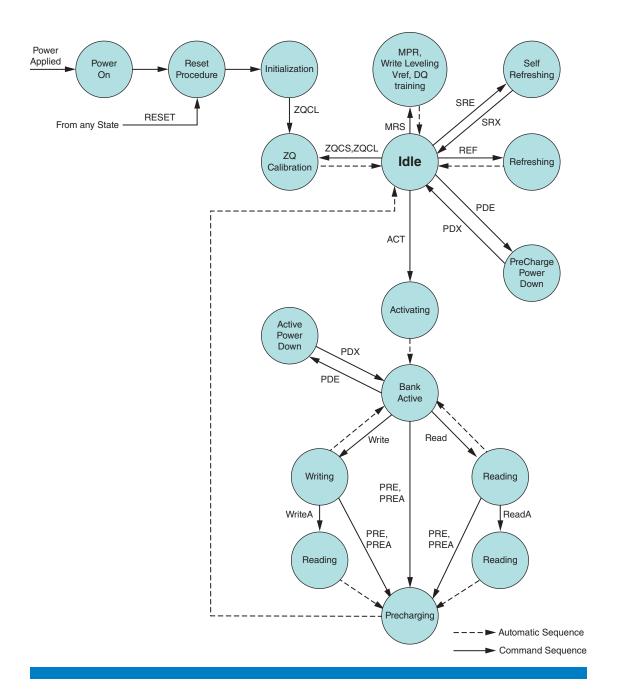

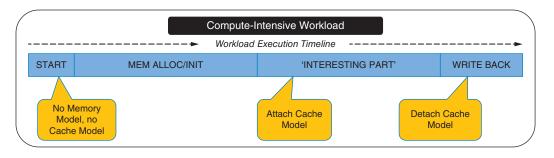

This initial state of platform hardware prior to BIOS execution will be referred to as the initialization state. The BIOS executes to initialize the rest of the hardware in preparation for the operating system to run. The state entered after BIOS has executed and prior to the operating system is running will be referred to as the *runtime state*. Refer to Figure 1.

Figure 1: Initialization vs. Runtime States (Source: Intel Corporation, 2013)

In the initialization state only minimal hardware components are initialized. The goal is to enable hardware components required to enable fetching and executing BIOS, such as:

- CPU cores are initialized

- A path to the BIOS flash is established

- Processor interconnects are initialized and available in slow speed mode with minimal routing

In the runtime state the hardware is fully functional for use by an operating system. All hardware components are discovered and configured. In this state several interfaces are transparent to the operating system and hidden by the system memory map:

- Socket interconnects

- Memory channels and interleaving

- Memory type and speed

- Hardware testing interfaces

Many software simulation tools can provide a platform-level simulation interface to support operating system and driver development. However, to support BIOS development the simulation tool must simulate the initialization state to a sufficient depth to support the configuration of a variety of hardware components

"1) In the initialization state only minimal hardware components are initialized.

2) In the runtime state the hardware is fully functional for use by an operating system."

"The implementation of memory spaces provides a mechanism to transition from initialization to runtime states."

that are not required (transparent) during the runtime state. In addition, to support a seamless boot with optimal performance the transition from initialization state to runtime state must be transparent to software and BIOS.

The Wind River Simics\* implementation of memory spaces<sup>[1]</sup> provides a mechanism that supports the transition of components from initialization to runtime. When instructions are executed they access addresses. These addresses are resolved using Simics memory spaces. If the address does not exist in the Simics memory space infrastructure, an error is reported. The dynamic nature of memory spaces allow them to be added and removed during the simulation run. This provides the ability to only add memory spaces after the underlying components have been fully initialized. More detail on how this mechanism is used to support BIOS development will be described in the section "Development and Debugging BIOS."

Key to transitioning between initialization and runtime states is verifying the initialization is completed per the hardware specification. In many cases registers can be written with incorrect values that will not be discovered on real hardware until much later, making debugging difficult. For example, hardware decoders are programmed by BIOS to enable access to memory. The hardware does not check to see if the decoders are programmed correctly. Consequently, if BIOS programs a memory decoder to point to nonexistent memory it will not be discovered until an application accesses the memory region resulting in a hardware machine check and system halt. Therefore, just modeling the components exactly matching hardware behavior is insufficient. The simulator must also add specific checks to verify registers were programmed correctly prior to switching to the runtime state.

# **Usage Models**

The two primary usage models for BIOS development are pre-silicon and postsilicon. Both environments present unique requirements on the simulation tool used.

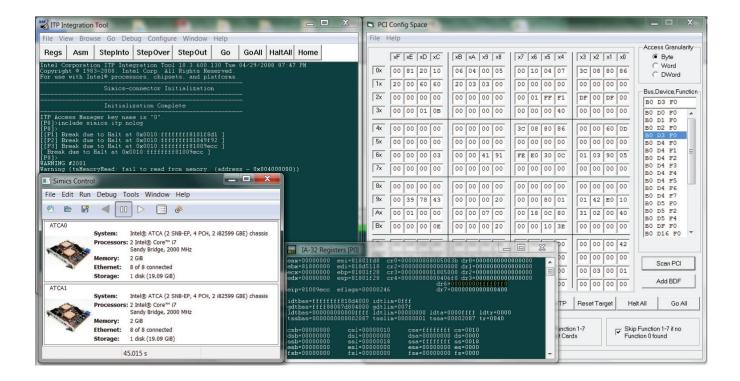

#### Pre-Silicon Usage Model

Pre-silicon validation is the activity of validating software prior to silicon availability. In a pre-silicon environment a variety of tools are available for BIOS development and debugging:

- Software simulation—Simulation tools focus on the functional model and

interfaces of the hardware platform. They are fast and easy to update to

accommodate the latest hardware changes. However, they usually do not

model timing characteristics and are less accurate.

- RTL (resistor-transistor logic) emulation—RTL emulator's use

programmed field-programmable gate arrays (FPGAs) to emulate the

hardware based on the RTL. These are very accurate models. However, they

are slow, expensive, and take time to update to the latest hardware changes.

- Pre-power on platforms—Pre-power on systems use interposers on existing platforms to allow for testing of components that have completed

- development. These systems are expensive, available in limited quantities, and require BIOS changes to use.

- BIOS support applications—These are applications developed by BIOS teams for specific point testing and data gathering. The primary function is to gather BIOS behavioral and flow information to be evaluated by design engineers for correctness (for example, an application that uses simple text file formats to take register input values and capture register output values from BIOS).

Consequently, due to cost and availability, the primary tool used for BIOS development and debugging in the pre-silicon environment is functional software simulation.

In this environment, hardware interfaces and feature sets can change frequently, requiring maximum flexibility in the simulation tool to quickly adapt to hardware specification changes. In addition, the development of the simulation tool is based on the same specifications as the BIOS development. Those specifications are usually not complete, so staged development is required and close coordination with the BIOS development team regarding

"The development of the simulation tool is based on the same specifications as the BIOS development."

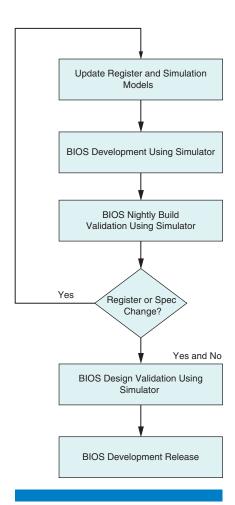

Figure 2: Pre-silicon BIOS development flow (Source: Intel Corporation, 2013)

feature set development and timelines is required (See Figure 2 for pre-silicon BIOS development flow). In this stage:

- The simulator is the primary BIOS development tool

- The functionality of the simulation tool is focused on supporting the hardware power-on configurations

- Validation teams use the simulator to pre-validate BIOS as well as the validation tests that will be run on hardware

- The BIOS team uses the simulator as a check-in criteria test for software check-in

To facilitate smooth BIOS development in a simulated environment, a mechanism is implemented to communicate between the BIOS and the simulator. The mechanism enables the BIOS to recognize it is running in a simulated environment and allow it to tell the simulation it is skipping sections of BIOS that are not developed. The mechanism consists of using an offset in PCI configuration space of a valid bus/device/function but where no register exists in real hardware. When queried on real hardware the register will return 0 per the PCIe specification requirements. However, on the simulator it will return a nonzero value to indicate the BIOS is running on the simulator. It also provides bit fields that can act as a means to communicate between BIOS and simulator-specific feature enabling.

#### This mechanism is used:

- To increase performance of BIOS boot by skipping delay loops required for booting on real hardware.

- To recognize a variety of environments, such as simulation and emulation.

- To work around features not yet developed in BIOS or the simulation on a temporary basis.

- To enable a single BIOS binary build that can run on hardware and the simulation.

- To provide a convenient mechanism to test a simulator's ability to run an unmodified BIOS at any time.

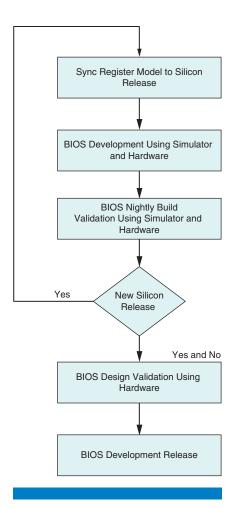

## Post-Silicon Usage Model

In the post-silicon environment hardware is available in limited quantities and configurations. The use of pre-power on systems is stopped and RTL emulation is slowed down. Early during the post-silicon phase the hardware availability and supported hardware configurations are limited. Consequently, the use of simulation continues:

- For those configurations not yet available in hardware

- In lieu of hardware availability

- Due to cost of power-on hardware

- In day-to-day BIOS development

"Early during the post-silicon phase the hardware availability and supported configurations are limited."

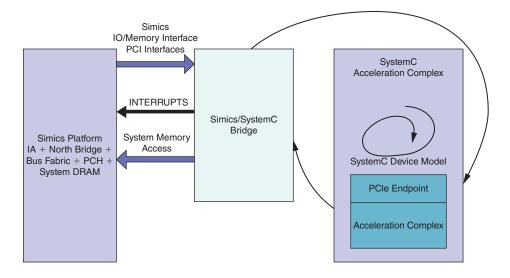

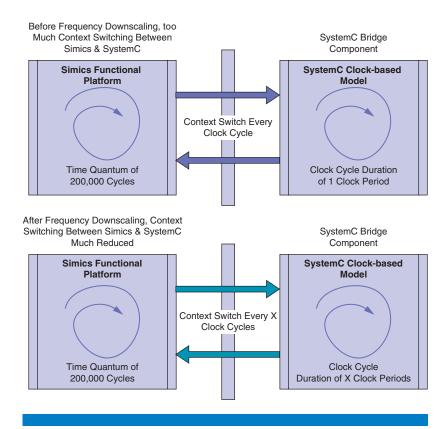

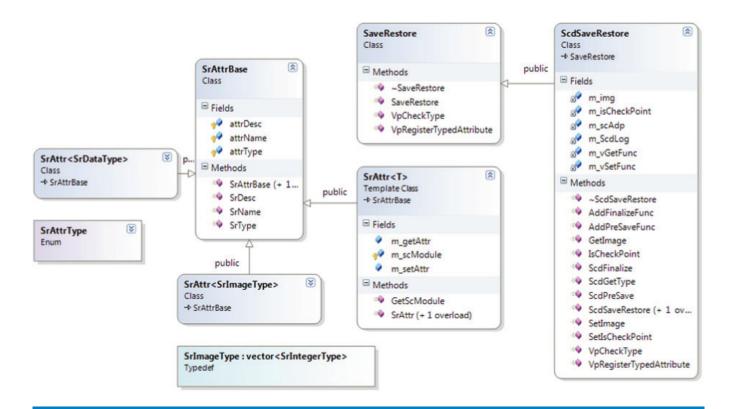

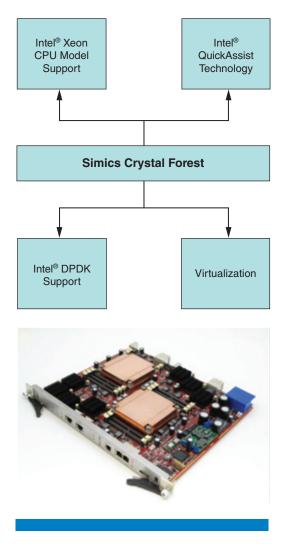

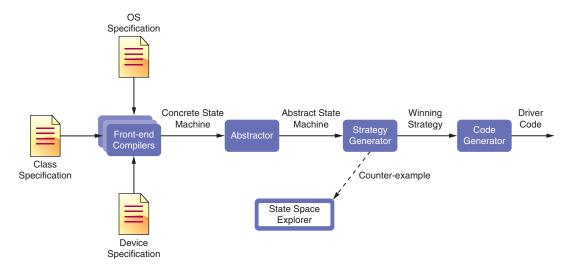

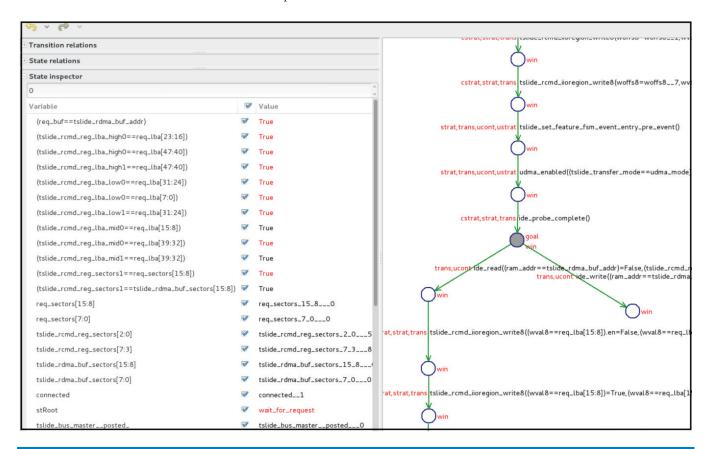

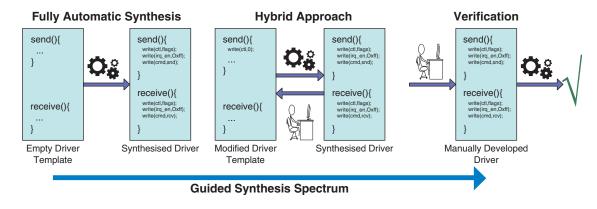

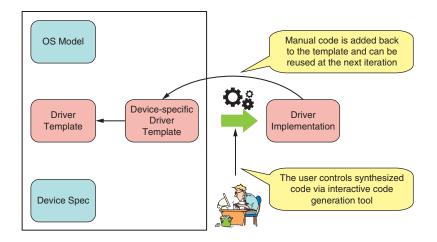

Figure 3: Post-silicon BIOS development flow (Source: Intel Corporation, 2013)